XCV200-6FG456C FPGA: Ominaisuudet, tekniset tiedot, ohjelmointi ja sovellukset

XCV200-6FG456C on tehokas FPGA (kenttäohjelmoitava porttiryhmä) AMD Xilinx VIREX® -sarjasta.Tämä opas selittää sen ominaisuudet, PIN -asettelun, ohjelmointivaiheet ja käyttötarkoitukset.Korkealla prosessointiteholla, joustavilla suunnitteluvaihtoehdoilla ja vahvalla syöttö-/lähtö- (I/O) ominaisuuksilla tämä FPGA auttaa rakentamaan nopeita ja luotettavia digitaalisia järjestelmiä.Työskentelet sitten verkottumista, ohjausjärjestelmiä tai mukautettua elektroniikkaa, tämä opas auttaa sinua ymmärtämään, kuinka XCV200-6FG456C: tä voidaan käyttää projektissasi.Luettelo

XCV200-6FG456C Yleiskatsaus

Se XCV200-6FG456C on merkittävä malli AMD Xilinx VIREX® FPGA -perheessä, joka on suunniteltu tarjoamaan vankat ohjelmoitavat logiikkaratkaisut monimutkaisille digitaalisille järjestelmille.Tämä erityinen siru kattaa noin 236 666 järjestelmäporttia ja siinä on 1 176 konfiguroitavaa logiikkalohkoa (CLBS) ja 5 292 logiikkakennoa.Se sisältää myös 57 344 RAM-bittiä ja tukee 284 I/O-nastat, jotka on sijoitettu 456-palloiseen hienolaunan pallokotiryhmään (FBGA) -pakettiin, jonka mitat ovat 23 mm 23 mm.Tämä malli toimii 2,5 V: n nimellisjännitteellä, jonka alue on 2,375 V - 2,625 V ja voi toimia lämpötila -alueella 0 ° C - 85 ° C.Laajempi VIREX® -sarja palvelee erilaisia sovelluksia, joiden tiheys on 50 000 - yli miljoonaan järjestelmäportit ja järjestelmän kellonopeudet jopa 200 MHz: iin.Se tukee muun muassa lukuisia I/O -standardeja, mukaan lukien LVTTL, LVCMOS ja PCI.Ominaisuudet, kuten viivealuetut silmukat (DLL), sulautetun muistin määrittämät logiikkapalikot ja aritmeettisten toimintojen omistettu logiikka parantavat sen toiminnallisuutta.Valmistettu käyttämällä 0,22 um 5-kerroksisella metalliprosessilla, VIREX®-perhe takaa suorituskyvyn ja luotettavuuden.

Jos haluat integroida ylimmän tason FPGA-tekniikkaa tuotteisiisi tai järjestelmiin, XCV200-6FG456C: n ostaminen irtotavarana on älykäs siirto.Se täyttää alan standardit ja pitää sinut eteenpäin tulevien teknologiatarpeiden edessä.

XCV200-6FG456C-ominaisuudet

Olla Järjestelmäportit: XCV200-6FG456C tarjoaa noin 236 666 järjestelmäporttia.Tämä korkea portin lukumäärä mahdollistaa monimutkaisten integroidun digitaalisen logiikkapiirin toteuttamisen yhdellä sirulla, mikä parantaa sekä suorituskykyä että monipuolisuutta monissa sovelluksissa.

Olla Logiikka resurssit: Se sisältää 1 176 konfiguroitavaa logiikkapalkkia (CLBS) ja 5 292 logiikkasolua.Nämä resurssit ovat hyviä joustavien ja skaalautuvien digitaalisten piirien suunnitteluun.CLB: t voidaan ohjelmoida suorittamaan monenlaisia loogisia funktioita, kun taas suuri määrä logiikkakennoja mahdollistaa laajojen logiikkatoimintojen ja prosessien käsittelyn.

Olla Muisti: Laite tarjoaa 57 344 bittiä RAM -muistia, jaetaan logiikkalohkoihinsa.Tätä sulautettua RAM-muistia käytetään sovelluksiin, jotka vaativat nopeaa ja tehokasta tiedon tallentamista ja hakua, mikä tukee nopeaa datanoperaatiota, joka on integroitu nykyaikaisiin digitaalisiin järjestelmiin.

Olla I/O -ominaisuudet: 284 syöttö-/lähtötaput XCV200-6FG456C helpottaa laajoja rajapintaominaisuuksia.Nämä I/O -nastat tukevat erilaisia signaalistandardeja ja antavat FPGA: lle mahdollisuuden kommunikoida tehokkaasti järjestelmän muiden komponenttien, kuten muistilaitteiden, prosessorien ja oheislaitteiden, kanssa.

Olla Jännite- ja lämpötila -alue: Toimii nimellisjännitteellä 2,5 V: llä, ja sen hyväksyttävä alue on 2,375 V-2,625 V, tämä FPGA on suunniteltu pienitehoiseen kulutukseen säilyttäen samalla vankan suorituskyvyn.Se voi toimia liitoslämpötila -alueella 0 ° C - 85 ° C, varmistaen luotettavuuden vaihtelevissa ympäristöolosuhteissa.

XCV200-6FG456C PIN-toimintokaavio

Se XCV200-6FG456C PIN-toimintokaavio on FPGA: n PIN -tehtävien jäsennelty esitys, joka on luokiteltu eri pankkeihin (Pankki 0 - pankki 7).Jokainen pankki ryhmittelee nastat toiminnan ja fyysisen sijoituksen perusteella FPGA -pakettiin.Numerointi- ja merkintäjärjestelmä noudattaa ruudukkokuviota, jossa rivejä merkitään kirjaimilla (A, B, C jne.) Ja sarakkeet numeroilla (1, 2, 3 jne.), Jotka helpottavat tiettyjen tapien nopeaa tunnistamista.Nämä pankit vastaavat erilaisia tulo-/lähtöfunktioita, tehoa, maa- ja omistettua signaalin reititystä.Nastat määritetään erilaisiin funktionaalisiin ryhmiin, mukaan lukien yleiskäyttöiset I/O (GPIO), jotka on usein merkitty nimellä "G" (yleinen tulo/lähtö), "V" (jännitteen syöttö) ja "O" (lähtö).Teho- ja maatapit on merkitty selvästi, mikä varmistaa vakaan FPGA -toiminnan.Erityiskäyttötapit, kuten kellotulot, nollaukset ja ohjaussignaalit, tunnistetaan symboleilla, kuten "R" tai "T..Jotkut nastat palvelevat myös omistettuja viestintärooleja, mukaan lukien JTAG-kokoonpano ja nopea kello, ohjelmointia ja virheenkorjausta varten.

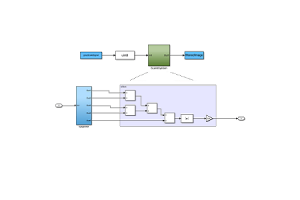

XCV200-6FG456C-lohkokaavio

Syöttö-/lähtölohko

Kaavio edustaa Tulo-/lähtölohko (IOB) XCV200-6FG456C FPGA: n rakenne, joka on Xilinx ViretEx -perheen jäsen.Kaavio esittelee tulo- ja lähtötoimintoihin liittyviä keskeisiä elementtejä korostaen datavirta- ja ohjausmekanismeja.Kaavion ytimessä käytetään kolme D-flipp-floppia syöttö-, lähtö- ja kolmen tilan ohjaamisen signaalien rekisteröimiseen.Lähtörekisteriä ohjataan OCE (lähtökello Enable) -signaalilla, joka määrittää, milloin lähtötiedot lukitaan.Samoin TRI-State-rekisteriä ohjataan TCE: llä (Tri-State Clock Enable), mikä mahdollistaa tai poistaa käytöstä lähtöpuskurin.Syöttörekisteri kaappaa saapuvat tiedot ja soveltaa ohjelmoitavaa viivettä ennen sen siirtämistä sisäiseen FPGA -logiikkaan IBUF: n (syöttöpuskurin) kautta.Obuft (Tri-State-lähtöpuskuri) varmistaa, että FPGA voi joko ajaa signaalin tyynylle (I/O-nasta) tai sijoittaa sen korkean impedanssitilaan ohjauslogiikasta riippuen.Heikko maalivahti piiri sisältyy tyynylle viimeisen tunnetun logiikkatilan ylläpitämiseksi, kun aktiivista ohjainta ei ole läsnä, mikä estää tahattomia kelluvia olosuhteita.Vertailujännitettä (VREF) käytetään tietyille syöttöstandardeille, kuten SSTL tai HSTL, jotka vaativat tarkkaa jännitetasoa oikeaa toimintaa varten.Kaiken kaikkiaan tämä IOB-rakenne antaa FPGA: lle mahdollisuuden hallita nopeaa tiedonsiirtoa, tukea erilaisia I/O-standardeja ja antaa joustavan hallinnan signaalin ajoituksesta ja eheydestä.

Master/orja -sarjatila

Se Master/orja -sarjatila Lohkokaavio kuvaa ViretEx FPGA: n, erityisesti XCV200-6FG456C: n, konfigurointiprosessia, kun se on ohjelmoitu päivänkakkaraketjun konfiguraatiossa käyttämällä sarja-EEPROM (XC1701L).Tässä asennuksessa yksi ViretEx -laite toimii päällikkönä, konfiguraatiokellon (CCLK) ohjaamisen ja konfigurointitietojen sarjan avulla ketjun ylimääräisiin orja -FPGA -tiedostoihin.Master FPGA aloittaa konfigurointiprosessin vakuuttamalla ohjelman signaalin palauttamalla kaikki ketjun laitteet.Kun alustaminen on valmis, init -signaali osoittaa valmiuden ja konfigurointitiedot virtaavat sarjan EEPROM (XC1701L) FPGA: n Din (data In) -tappiin.Master FPGA lukee tietoja EEPROM: sta ja välittää sen DOUT: n (datan) kautta seuraaviin orja -FPGA: iin synkronoimalla tiedonsiirron CCLK -signaalin avulla.Valitettua signaalia käytetään osoittamaan onnistunut kokoonpano, valinnaisella vetovastuksella varmistaen vakaan korkean tilan, kun kokoonpano on valmis.XC1701L EEPROM -sovellusta hallitsee pää FPGA CLK-, Data-, CE (ChIP Enable) ja Reset/OE (Output Enable) -signaalien avulla, varmistaen, että tallennettu konfigurointitieto haetaan oikein.Tämä konfiguraatiomenetelmä on tehokas useiden FPGA -ohjelmien ohjelmoimiseksi käyttämällä yhtä EEPROM: ää, vähentämällä ulkoista johdotuksen monimutkaisuutta ja varmistamalla, että kaikki laitteet vastaanottaa synkronoituja konfigurointitietoja.

XCV200-6FG456C-tekniset tiedot

|

Tyyppi |

Parametri |

|

Valmistaja |

AMD Xilinx

|

|

Sarja |

ViretEx® |

|

Pakkaus |

Tarjotin |

|

Osien tila |

Vanhentunut |

|

Laboratorioiden lukumäärä |

1176 |

|

Logiikkaelementtien/solujen lukumäärä |

5292 |

|

RAM -bittiä |

57344 |

|

I/O: n lukumäärä |

284 |

|

Porttien lukumäärä |

236666 |

|

Jännite - Syöttö |

2,375V ~ 2,625 V |

|

Asennustyyppi |

Pintakori |

|

Käyttölämpötila |

0 ° C ~ 85 ° C (TJ) |

|

Paketti / kotelo |

456-BBGA |

|

Toimittajan laitepaketti |

456-FBGA (23x23) |

|

Perustuotteenumero |

XCV200 |

XCV200-6FG456C-sovellukset

Televiestintä ja verkottuminen

XCV200-6FG456C on edennyt tietoliikenteessä ja verkkosovelluksissa, koska se kykenee käsittelemään nopeaa tiedonsiirtoa ja monimutkaisia signaalinkäsittelytehtäviä.Sen korkea portin lukumäärä ja vankka I/O -ominaisuudet antavat sen tukea toimintoja, kuten paketin käsittelyä, signaalin modulaatiota/demodulaatiota ja virheenkorjausprotokollia.

Digitaalinen signaalinkäsittely (DSP)

Ihanteellinen DSP -sovelluksiin, tämä FPGA voi suorittaa ään- ja videoiden käsittelytekniikassa tarvittavat nopeat ja monimutkaiset matemaattiset laskelmat.Olipa kyse multimediajärjestelmistä, äänentunnistuksesta tai suoratoistopalveluista, XCV200-6FG456C: n tehokkaista käsittelyominaisuuksista ja sulautetuista muistista tukevat tehokasta ja korkealaatuista signaalinkäsittelyä.

Teollisuusjärjestelmät

Teollisuusautomaatiossa XCV200-6FG456C tarjoaa tarvittavan suorituskyvyn ohjausjärjestelmien ja automaatioverkkojen hallintaan.Sen kyky suorittaa useita ohjaustehtäviä samanaikaisesti samalla kun vasteajat tekevät siitä sopivan sovelluksiin prosessinhallinnassa, robotiikassa ja konevisiossa.

Lääketieteelliset välineet

FPGA: n tarkkuus ja nopeus ovat hienoja lääketieteellisissä kuvantamis- ja diagnostisissa laitteissa, joissa se auttaa monimutkaisten algoritmien käsittelyä kuvantamissovelluksiin, kuten MRI-, ultraääni- ja CT -skannauksiin.XCV200-6FG456C: n ominaisuudet varmistavat, että se pystyy käsittelemään korkean datan läpimenon ja monimutkaisen prosessoinnin, jota tarvitaan nykyaikaisessa lääketieteellisessä tekniikassa.

Xcv200-6fg456c samanlaisia osia

Olla XCV2000E-6BG560C

Olla XCV200-6FG256C

Olla XCV200-5FG256C

XCV200-6FG456C-ohjelmointivaiheet

XCV200-6FG456C: lle ohjelmointivaiheet:

1. Suunnittelutieto

FPGA -ohjelmoinnin alkuvaihe sisältää järjestelmän digitaalisen logiikan ja toiminnallisuuden määrittelyn.Tämä voidaan tehdä käyttämällä laitteistokuvauksia (HDLS), kuten VHDL tai Verilog, jossa kirjoitat koodia, joka määrittelee, kuinka FPGA käsittelee tietoja ja on vuorovaikutuksessa muiden laitteistojen kanssa.FPGA -suunnitteluohjelmistoissa, kuten Xilinx ISE tai Vivado, saatavilla voidaan käyttää kaavamaisia pääsytyökaluja.Tämä menetelmä sisältää logiikan visuaalisen esityksen luomisen vetämällä ja pudottamalla komponentteja, jotka jotkut pitävät intuitiivisempia kuin kirjoituskoodi.

2. Synteesi

Kun suunnittelu on valmis, seuraava vaihe on synteesi, jossa Xilinxin XST (Xilinx -synteesitekniikka) kaltainen työkalu muuttaa HDL -koodin tai kaavamaisen suunnittelun verkkoluetteloksi.Tämä verkkoluettelo kuvaa piiriä geneeristen digitaalisten komponenttien, kuten logiikkaporttien ja rekistereiden suhteen.Synteesiprosessiin sisältyy myös suunnittelun optimointi suorituskykyvaatimusten täyttämiseksi ja resurssien käytön minimoimiseksi tehokkaaseen FPGA -toimintaan.

3. Toteutus

Toteutusprosessi alkaa käännöksellä yhdistämällä suunnittelusi rajoitustiedostoihin, jotka määrittelevät parametrit, kuten kellotaajuudet ja PIN -määritykset.Käännöksen jälkeen kartoitusvaihe antaa verkkosi elementit FPGA: n tietyille fyysisille resursseille, kuten hakupöydät (LUT) ja flip-flops.Sijoittelu- ja reititysvaihe määrittelee sitten kunkin komponentin fyysiset sijainnit FPGA: n arkkitehtuurissa ja muodostaa yhteydet niiden välillä ohjelmoitavien toisiinsa liittyvien resurssien avulla.Tämä vaihe on hieno saavuttamaan halutut suorituskykymittarit, mukaan lukien kellotaajuudet.

4. BITSTREA -sukupolvi

Onnistuneen sijoittamisen ja reitityksen jälkeen työkalu luo bittReam, binaarisen määritystiedoston, joka sisältää kaikki FPGA: n ohjelmointitiedot.Usein on suositeltavaa simuloida lopullista suunnittelua sijoittamisen jälkeen varmistaaksesi, että bittivirta käyttäytyy odotetusti olosuhteissa.Tämä varmennusvaihe auttaa välttämään mahdollisia ongelmia todellisen toiminnan aikana.

5. Kokoonpano

Viimeiseen vaiheeseen sisältyy bittivirran lataaminen FPGA: hon käyttämällä erilaisia konfigurointimenetelmiä.Orja-sarjan tila, yksinkertainen ja kustannustehokas vaihtoehto, määrittää FPGA: n ulkoisen päälaitteen kautta, joka lähettää tietoja sarjassa.Master-tilassa FPGA lukee itsenäisesti bittivirran liitteenä olevasta sarjasta.Nopeuskokoonpanoissa SelectMap-tila antaa ulkoisen mikroprosessorin ladata tietoja nopeasti FPGA: hon.Lisäksi JTAG-tilaa käytetään paitsi ohjelmointiin myös testaamiseen ja virheenkorjaukseen, standardirajapinnan hyödyntämiseen järjestelmän sisäiseen ohjelmointiin ja raja-skannaustestaukseen.

XCV200-6FG456C Edut

Suorituskyky

Xilinx ViretEx -sarja, johon XCV200-6FG456C kuuluu, on optimoitu nopeaan suorituskykyyn, tarjoamalla järjestelmän kellotason jopa 200 MHz.Tämä tekee siitä hyvin soveltuvan sovelluksille, jotka vaativat nopean tietojenkäsittelyn, varmistaen monimutkaisten algoritmien ja nopean toiminnan tehokkaan käsittelyn, kuten televiestintä, prosessointi ja multimedia.

I/O -standardien tuki

Tämä FPGA tukee laajaa valikoimaa syöttö-/lähtöstandardeja, mukaan lukien LVTTL, LVCMOS, PCI, GTL, HSTL, SSTL, CTT ja AGP.Tällainen laaja I/O-standardien tuki antaa XCV200-6FG456C: lle integroida saumattomasti erilaisiin järjestelmän komponentteihin, mikä parantaa sen hyödyllisyyttä erilaisissa digitaalisissa ekosysteemeissä.Tämä joustavuus mahdollistaa FPGA: n mukauttamisen erilaisiin rajapintaolosuhteisiin ilman järjestelmän modifikaatioita.

Kellonhallinta

XCV200-6FG456C sisältää useita viivealueisia silmukoita (DLL) kellon jakelua ja hallintaa varten järjestelmässä.Nämä DLL: t auttavat parantamaan järjestelmän ajoitusta ja luotettavuutta tarjoamalla tarkat kellonsignaalit, jotka ovat välttämättömiä synkronisiin toimintoihin.Tämä ominaisuus on tärkeä vähentämällä järjestelmävirheitä ja parantamalla yleistä suorituskykyä, etenkin monimutkaisissa malleissa, jotka vaativat tarkkaa ajoitusta ja synkronointia.

Suunnittelun joustavuus

XCV200-6FG456C tarjoaa 1,176 konfiguroitavissa olevilla logiikkalohkoilla ja 5 292 logiikkakennolla huomattavia logiikka resursseja, joilla on kyky toteuttaa monipuolinen toiminto.Yksinkertaisesta liimalogiikasta monimutkaisiksi digitaalisiin järjestelmiin tämä FPGA tukee monimutkaisia suunnitteluvaatimuksia, mikä tekee siitä ihanteellisen sovelluksille mukautetussa laskennassa, digitaalisen signaalinkäsittelyssä ja prototyyppien määrittämisessä.

Nopea prototyyppi

FPGA: t, kuten XCV200-6FG456C, on tunnettu kyvystä tukea nopeaa prototyyppiä.Tämä laite mahdollistaa nopean suunnittelun iteraatiot ja voidaan määrittää uudelleen kentällä, mikä on etukehityssyklien etu, koska se vähentää markkinoita koskevia aikaa.Se mukautuu tehokkaasti myös vaatimusten muuttamiseen tai päivityksiin projektivaatimuksissa varmistaen, että lopputuotteet ovat ajan tasalla uusimpien teknologisten standardien kanssa.

Integrointikyky

XCV200-6FG456C: n integraatioominaisuudet helpottavat useiden erillisten komponenttien yhdistämistä yhdeksi siruksi.Tämä integrointi voi johtaa järjestelmän monimutkaisuuteen, alhaisempaan virrankulutukseen ja kustannussäästöihin.Minimoimalla tarvittavien erillisten komponenttien lukumäärä, tämä FPGA yksinkertaistaa suunnitteluprosesseja ja parantaa kokonaisjärjestelmän luotettavuutta ja kompaktiisuutta.

XCV200-6FG456C-pakkausmitat

XCV200-6FG456C on AMD: n VIRTEX®-sarjan kenttäohjelmoitava porttijärjestelmä (FPGA), joka on sijoitettu 456-pallon hienovallaripalloruudukkoon (FBGA) -pakettiin.

Olla Pakettityyppi: 456-FBGA

Olla Pakkauskoko: 23 mm x 23 mm

Olla Pallokorkeus: 1,0 mm

XCV200-6FG456C Valmistaja

XCV200-6FG456C on kenttäohjelmoitava porttijärjestelmä (FPGA), jonka on alun perin kehittänyt Xilinx, yritys, joka tunnetaan korkean suorituskyvyn ohjelmoitavista logiikkalaitteistaan.Xilinxin hankkimisen jälkeen AMD, XCV200-6FG456C liittyy nyt AMD: hen sen nykyisenä valmistajana.Tämä FPGA -malli on kuitenkin vanhentunut eikä enää tuotannossa.AMD tukee edelleen uudempia FPGA -arkkitehtuureja, joilla on parantunut suorituskyky, tehon tehokkuus ja laajennettu pitkäikäisyys, mikä tekee nykyaikaisista vaihtoehdoista parempia uusille malleille.

Johtopäätös

XCV200-6FG456C on monipuolinen ja nopea FPGA, joka on hyödyllinen monille teknologiasovelluksille.Vaikka sitä ei enää tehdä, se on silti hyvä valinta vanhemmille järjestelmille, jotka tarvitsevat luotettavaa suorituskykyä.Tämä opas on kattanut suunnittelunsa, ohjelmointivaiheet ja käytännölliset käytöt, mikä on helpompaa ymmärtää, miten se toimii ja miten sitä voidaan käyttää.Kun uudemmat FPGA: t tulevat saataville, voit käyttää tätä tietoa valitaksesi oikean FPGA: n tarpeisiisi ja parantaa digitaalisia malleja.

Tietotarvikkeet PDF

XCV200-6FG456C Datarstateetit:

Meistä

ALLELCO LIMITED

Lue lisää

Nopea kysely

Lähetä kysely, vastaamme heti.

Usein Kysytyt Kysymykset [FAQ]

1. Mikä on XCV200-6FG456C: n virrankulutus?

XCV200-6FG456C toimii 2,5 V: llä, jännitealueella 2,375 V-2,625 V.Virrankulutus riippuu logiikan käytöstä ja kellotaajuudesta, mutta vanhempana FPGA: na voi olla vähemmän tehotehokas kuin uudemmat Xilinx-laitteet.Oikea voimanhallinta ja lämmön hajoaminen tulisi harkita.

2. Kuinka XCV200-6FG456C verrataan XCV200-6FG256C: hen?

XCV200-6FG456C: llä on suurempi paketti (456-pallo FBGA) verrattuna XCV200-6FG256C (256-Ball FBGA), joka tarjoaa enemmän I/O-nastaa (284 vs. 172) ja mahdollisesti parempaa suorituskykyä sovelluksille, jotka vaativat laajaa käyttöliittymää.Jos suunnittelusi riippuu enemmän I/O-ominaisuuksista, XCV200-6FG456C on parempi valinta.

3. Voinko ohjelmoida XCV200-6FG456C uudelleen useita kertoja?

Kyllä, XCV200-6FG456C on SRAM-pohjainen FPGA, mikä tarkoittaa, että se voidaan ohjelmoida uudelleen rajoittamattoman määrän kertoja niin kauan kuin virtaa toimitetaan.Tarvitset kuitenkin ulkoista haihduttamatonta muistia (EEPROM tai Flash) säilyttääksesi bitstreamit virtasyklin jälkeen.

4. Tukeeko XCV200-6FG456C nopeaa sarjaviestintää?

XCV200-6FG456C tukee useita I/OTarkastele uudempia FPGA-malleja sovelluksiin, jotka vaativat nopeaa sarjalinkkejä (esim. PCIE, Gigabit Ethernet tai HDMI).

5. Kuinka XCV200-6FG456C verrataan uudempiin FPGA-malleihin?

XCV200-6FG456C kuuluu vanhempaan FPGA-sukupolveen.Verrattuna nykyaikaiseen VIREX FPGA -sovellukseen, sillä on alhaisempi portin määrä, hitaampi kellonopeus ja rajoitettu tehotehokkuus.Uudemmat mallit tarjoavat korkeamman logiikkatiheyden, upotetun muistin, edistyneiden DSP -lohkojen ja pienemmän virrankulutuksen, mikä tekee niistä parempia nykyaikaisissa sovelluksissa.

Ad73322ar -pinout, ominaisuudet ja tekniset yksityiskohdat selitetyt

21.03.2025

EP20K100EFC324-1X FPGA: Ominaisuudet, tekniset tiedot, sovellukset ja ohjelmointiopas

20.03.2025

Suositut viestit

-

COMPLECT -ohjeet Tietokoneet: Kuinka ne muuttivat tietojenkäsittelyä?

18.04.8000 147760

-

USB-C-pinout ja ominaisuudet

18.04.2000 111974

-

Xilinx Unified Simulation Primitive -sovelluksen käyttäminen: Kattava opas FPGA: n suunnitteluun ja simulointiin

18.04.1600 111351

-

Virtalähteen jännitteet elektroniikassa: VCC:n, VDD:n, VEE:n, VSS:n ja GND:n merkitys

18.04.0400 83742

-

RJ45 Connector Guide: Pinout, johdotus, kaapelityypit ja käyttö

01.01.1970 79527

-

Lopullinen opas johdon värikoodiin nykyaikaisissa sähköjärjestelmissä

Tapa, jolla sähköjärjestelmämme käyttävät värejä, ei ole vain ulkonäölle.Jokainen lankaväri osoittaa nyt tietyn toiminnon, mikä helpottaa sähkökomponenttien tunnistamista ja käsittelyä oikein asenn...01.01.1970 66937

-

Puhdistusventtiilin opas: Toiminta, oireet, testaus ja korvaava moottorin optimaalinen suorituskyky

Puhdistusventtiili on keskeinen osa auton järjestelmää, joka auttaa pitämään ilman puhtaana hallitsemalla polttoainehöyryjä ennen kuin ne voivat paeta ilmakehään.Tämä ei vain auta ympäristöä vähent...01.01.1970 63086

-

Laatu (Q) tekijä: Yhtälöt ja sovellukset

Laatukerroin tai 'Q' on tärkeä tarkistettaessa, kuinka hyvin induktorit ja resonaattorit toimivat elektronisissa järjestelmissä, jotka käyttävät radiotaajuuksia (RF).'Q' mittaa kuinka hyvin piiri m...01.01.1970 63025

-

Huippututkinnon saavuttaminen suurimmalla tehonsiirtolauseella

Suurin virransiirtolause selittää, kuinka energia lähteestä, kuten akku tai generaattori, virtaa kytkettyyn kuormaan.Se näyttää tarkan tilan, jossa kuorma vastaanottaa eniten virtaa.Tämä artikkeli ...01.01.1970 54092

-

A23 -akun tekniset tiedot ja yhteensopivuus

A23-akku on pieni, sylinterimainen akku, jolla on korkea jännite.Kutsutaan myös 23a, 23ae tai MN21, se toimii 12 voltilla ja paljon korkeampi kuin AA- tai AAA -akut.Sen erityinen muotoilu ...01.01.1970 52167