HDL: Innovaatioiden lukituksen avaaminen digitaalisen piirin suunnittelussa

Tämä opas tutkii laitteistokuvauskieliä (HDLS), tärkeitä työkaluja abstraktien malleiden muuttamiseksi todellisiksi, valmistettavissa oleviksi piireiksi.Käsittelemme niiden kehitystä, ASIC- ja FPGA -sovelluksia ja niiden vaikutuksia nykyaikaiseen elektroniikkaan.Esimerkkien ja asiantuntijoiden näkemysten avulla tämän oppaan tavoitteena on syventää ymmärrystäsi HDL: stä ja vahvistaa sekä teoriasi että käytännön taitojasi.Tutustu kuinka HDLS ylittää kuilun ideoiden ja fyysisten laitteiden välillä, ajaa innovaatioita tekniikassa.Luettelo

HDL: n rooli digitaalisessa suunnittelussa

Laitteiden kuvauskieli (HDL) on rooli digitaalisten järjestelmien suunnittelussa tarjoamalla jäsennelty tapa mallintaa monimutkaisia piirejä.Se mahdollistaa suurten järjestelmien hajottamisen pienempiin, hallittavissa oleviin moduuleihin, jotka testataan ja varmennetaan käyttämällä elektronisen suunnittelun automaatiotyökaluja.Kun nämä moduulit syntetisoidaan porttitason netlistoiksi, ja ne muutetaan fyysisiksi piireiksi ASIC- tai FPGA-sijoituksen ja reitityksen kautta.HDL -innovaatioiden kaltaisilla teollisuudenaloilla laajasti Alan teollisuudenaloilla auttamalla tasapainottamalla suunnittelurajoituksia luovien ratkaisujen kanssa, mikä tekee siitä avainkomponentin digitaalitekniikan edistämisessä.

HDL: n historiallinen kehitys

Laitteistokuvauskielten (HDLS) kehittäminen kattaa vuosikymmeniä, jotka kehittyvät hajanaisista, kapeasta työkalusta standardoituihin, teollisuudenlaajuisiin ratkaisuihin, kuten VHDL ja Verilog, 1980-luvun lopulla.Nämä standardisoidut HDLS: n yhtenäiset suunnittelukäytännöt ja parannettu yhteistyö.Teknologian edistyneessä HDLS laajeni tukemaan monimutkaisempia järjestelmiä, sillata laitteistoa ja ohjelmistosuunnittelua uusilla kielillä, kuten SystemC ja Superlog.HDLS on osoittanut arvonsa parantamalla viestintää, vähentämällä virheitä ja suunnitteluprosessin virtaviivaistamisessa.HDLS: n jatkuva kehitys heijastaa jatkuvan innovaation tarvetta vastaamaan digitaalisen suunnittelun muuttuvia vaatimuksia nykyaikaisen tekniikan kehittämiselle.

Tarkoitus

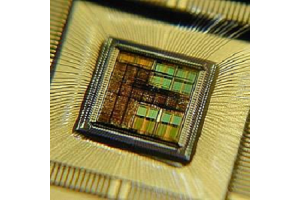

Koska integroidut piirit ovat kasvaneet monimutkaisemmiksi Mooren laki 1970-luvulta lähtien, suunnittelumenetelmät ovat siirtyneet keskittymisestä yksittäisiin komponentteihin järjestelmän tason tiedonkulun ja ajoituksen hallintaan.Tämä muutos johti rekisterinsiirtotason (RTL) abstraktion käyttöönottoon, jonka avulla voidaan keskittyä logiikkatoimintoihin ja ajoitukseen tarvitsematta käsitellä valmistustietoja jo varhain.RTL -abstraktio, jota tukee laitteistokuvauskielet (HDLS), virtaviivaistaa suunnitteluprosessia tasapainottamalla suorituskykyä, voimaa ja skaalautuvuutta.Se vähentää suunnittelusyklejä, parantaa yhteistyötä ja auttaa ennakoimaan mahdollisia ongelmia estämällä kalliita tarkistuksia.Keskittymällä korkeampaan abstraktiotasoon avaat suuremman tehokkuuden, sopeutumiskyvyn ja innovaatiot nopeasti kehittyvässä teknologiamaisemassa.

Rakenteelliset ominaisuudet

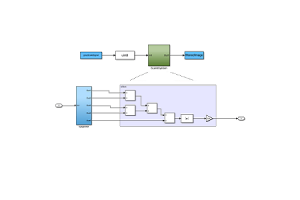

Laitteiden kuvauskielet (HDLS) toimivat tekstikehyksinä, jotka määrittelevät piirijärjestelmien rakenteen, käyttäytymisen ja ajoituksen.Ne toimivat kuin rinnakkaisohjelmointikielet, mutta ne on erityisesti suunnattu ajoituksen ja laitteistoyhteyksien hallintaan.HDL: t toimivat eri abstraktiotasojen, rakenteellisten, käyttäytymis- ja rekisterinsiirron välillä lähestyäkseen piirin suunnittelua eri näkökulmista.Rakenteellisella tasolla HDLS -yksityiskohtaiset komponentit ja yhteydet, samoin kuin kaaviot.Käyttäytymistaso keskittyy siihen, mitä piirin tulisi tehdä, kun taas rekisterinsiirtotaso (RTL) kuvaa tiedonkulkua ja toimintoja rekistereiden välillä, tasapainotustoiminnot ja laitteistotiedot.HDLS tukee myös logiikkasynteesiä, muuntamalla korkean tason mallit porttitason piireiksi ja simulaation, joka testaa toiminnallisuutta ennen laitteiston käyttöönottoa.Toisin kuin perinteiset ohjelmointikielet, HDL: t ovat ensisijaisesti mallinnustyökaluja, jotka kuvaavat laitteistokäyttäytymistä, mikä tekee niistä tärkeitä tarkan, innovatiivisen piirisuunnittelun kannalta.

Tietovirran tutkiminen HDL: ssä

Toisin kuin perinteiset ohjelmointikielet, jotka priorisoivat ohjausvirtauksen, HDLS keskittyy tiedonkulun mallintamiseen ja piireissä ajoitukseen laitteistojen kehittämiseen ja simulointiin.Tämä ainutlaatuinen kyky kaapata laitteistojen ajallinen käyttäytyminen HDLS: n kielistä, kuten C ++.Nykyaikaiset HDL: t, kuten Systemverilog, sekoittavat yhä enemmän ohjelmointiparadigmeja, jotka sisältävät oliokeskeisiä käsitteitä modulaarisuuden ja ylläpidettävyyden parantamiseksi monimutkaisissa järjestelmäsuunnissa.HDL: llä on myös rooli logiikan synteesissä, muuttamalla korkean tason kuvaukset porttitason toteutuksiksi varmistaen, että abstraktit mallit ovat yhdenmukaisia fyysisten rajoitusten kanssa.Lisäksi simulointiin ja todentamiseen käytetään syntetisoimattomia HDL-elementtejä piirin käyttäytymisen tiukasti ennen tuotantoa.Kun HDL: t kehittyvät edelleen, ne todennäköisesti omaksuvat enemmän ohjelmiston kaltaisia ominaisuuksia kasvavien laitteistojen monimutkaisuuksien ratkaisemiseksi, mikä kattaa kuilun laitteiston tarkkuuden ja ystävällisen abstraktion välillä.

Integroidun piirisuunnittelun parantaminen HDL: llä

Laitteistokuvauskielet (HDLS) virtaviivaistaa monimutkaista prosessia integroiduiden piirien suunnittelussa muuttamalla abstrakteja ideoita käytännöllisiksi, suoritettaviksi suunnitelmiksi.Monet käyttävät usein vuokaavioita ja tilakaavioita piirilogiikan kartoittamiseen ennen sen muuntamista tarkkaan HDL -koodiksi, aivan kuten rakennussuunnitelmien luominen.Piirivaatimusten noudattamisen yhteydessä toiset tuovat ainutlaatuisen tyylinsä koodaukseen sisällyttämällä algoritmeja ja skriptin toistuvien tehtävien yksinkertaistamiseksi.Virheen tarkistustyökalut tunnistavat sitten ongelmat varhain, varmistaen luotettavuuden ennen synteesiä.Synteesin jälkeen netlistat valmistetaan valmistukseen, joko FPGA: lle tai ASIC: lle, keskittyen laitteen eritelmiin tuotantohaasteiden välttämiseksi.HDL: t saavuttavat tasapainon luovuuden ja tarkkuuden välillä, mikä mahdollistaa innovatiiviset, mutta luottavat piirimallit, jotka etenevät tehokkaasti konseptista fyysiseen toteutumiseen.

Meistä

ALLELCO LIMITED

Lue lisää

Nopea kysely

Lähetä kysely, vastaamme heti.

VITIS Unified -ohjelmistoalusta: Sulautettujen järjestelmien ja mukautuvan laskennan kiihdyttäminen Xilinxin kanssa

07.01.2025

VLSI -tekniikan kehitys ja strateginen kehitys

06.01.2025

Suositut viestit

-

COMPLECT -ohjeet Tietokoneet: Kuinka ne muuttivat tietojenkäsittelyä?

19.04.8000 147784

-

USB-C-pinout ja ominaisuudet

19.04.2000 112077

-

Xilinx Unified Simulation Primitive -sovelluksen käyttäminen: Kattava opas FPGA: n suunnitteluun ja simulointiin

19.04.1600 111352

-

Virtalähteen jännitteet elektroniikassa: VCC:n, VDD:n, VEE:n, VSS:n ja GND:n merkitys

19.04.0400 83844

-

RJ45 Connector Guide: Pinout, johdotus, kaapelityypit ja käyttö

01.01.1970 79648

-

Lopullinen opas johdon värikoodiin nykyaikaisissa sähköjärjestelmissä

Tapa, jolla sähköjärjestelmämme käyttävät värejä, ei ole vain ulkonäölle.Jokainen lankaväri osoittaa nyt tietyn toiminnon, mikä helpottaa sähkökomponenttien tunnistamista ja käsittelyä oikein asenn...01.01.1970 67019

-

Puhdistusventtiilin opas: Toiminta, oireet, testaus ja korvaava moottorin optimaalinen suorituskyky

Puhdistusventtiili on keskeinen osa auton järjestelmää, joka auttaa pitämään ilman puhtaana hallitsemalla polttoainehöyryjä ennen kuin ne voivat paeta ilmakehään.Tämä ei vain auta ympäristöä vähent...01.01.1970 63140

-

Laatu (Q) tekijä: Yhtälöt ja sovellukset

Laatukerroin tai 'Q' on tärkeä tarkistettaessa, kuinka hyvin induktorit ja resonaattorit toimivat elektronisissa järjestelmissä, jotka käyttävät radiotaajuuksia (RF).'Q' mittaa kuinka hyvin piiri m...01.01.1970 63071

-

Huippututkinnon saavuttaminen suurimmalla tehonsiirtolauseella

Suurin virransiirtolause selittää, kuinka energia lähteestä, kuten akku tai generaattori, virtaa kytkettyyn kuormaan.Se näyttää tarkan tilan, jossa kuorma vastaanottaa eniten virtaa.Tämä artikkeli ...01.01.1970 54099

-

A23 -akun tekniset tiedot ja yhteensopivuus

A23-akku on pieni, sylinterimainen akku, jolla on korkea jännite.Kutsutaan myös 23a, 23ae tai MN21, se toimii 12 voltilla ja paljon korkeampi kuin AA- tai AAA -akut.Sen erityinen muotoilu ...01.01.1970 52233