EP2S60F672C4 FPGA: Ominaisuudet, sovellukset, ohjelmointi- ja tietotapaopas

Tässä oppaassa saat selkeän yleiskuvan EP2S60F672C4: stä, joka on Intelin Stratix II -perheen tehokas FPGA.Opit sen pääominaisuuksista, arkkitehtuurista, estorakenteesta ja teknisistä tiedoista ymmärtääksesi kuinka se sopii edistyneisiin digitaalisiin malliin.Se käy myös läpi ohjelmointivaiheen, sovellukset, edut ja haitat, jotta näet tarkalleen missä ja miten tätä laitetta voidaan käyttää.Luettelo

Mikä on EP2S60F672C4?

Se EP2S60F672C4 on Intelin (entinen Altera) korkean tiheys FPGA, joka kuuluu Stratix II -perheeseen.Se on rakennettu 90 nm, 1,2 V Copper SRAM -prosessiin, ja se tarjoaa huomattavan logiikkakapasiteetin 672-palloisessa FBGA-paketissa, mikä tekee siitä ihanteellisen monimutkaisten digitaalisten järjestelmien kanssa.Osana EP2S-sarjaa ”60” -laite sijaitsee Stratix II -kokoonpanon puolivälissä yläpuolelle ja tarjoaa vahvan logiikan tiheyden, sulautetun muistin ja I/O-resurssien tasapainon.Tämä FPGA tunnetaan vankasta arkkitehtuuristaan ja luotettavuudestaan edelleen luotettava valinta monissa edistyneissä malleissa.

Etsitkö EP2S60F672C4?Ota yhteyttä tarkistaaksesi nykyisen varastot, läpimenoaika ja hinnoittelu.

EP2S60F672C4 CAD -mallit

EP2S60F672C4 -symboli

EP2S60F672C4 Jalanjälki

EP2S60F672C4 3D -malli

EP2S60F672C4 -ominaisuudet

Olla Edistynyt 90 nm, 1,2 V CMOS -prosessi

EP2S60F672C4 on valmistettu 90 nm: n kaikkien kerroksen kuparikertomus CMOS-prosessissa, joka toimii 1,2 V: n ydinjännitteellä.Tämä tekniikka mahdollistaa suuren nopeuden, vähentyneen virrankulutuksen ja suuremman logiikan tiheyden verrattuna vanhempiin FPGA -sukupolviin.

Olla Adaptive Logic Module (ALM) -arkkitehtuuri

Laite käyttää almusta logiikka -rakennuspalikkaansa perinteisten logiikkaelementtien sijasta.Tämä arkkitehtuuri parantaa resurssien käyttöä, mikä mahdollistaa monimutkaisempien logiikkatoimintojen toteuttamisen tehokkaasti samalla piidialueella.

Olla Korkea logiikan tiheys

Noin 60 440 logiikkaelementtiä (24 176 almusta) FPGA tukee suuria ja hienostuneita digitaalisia malleja.Tämä suuri kapasiteetti tekee siitä sopivan sovelluksiin, kuten signaalinkäsittely-, viestintä- ja sulautettuihin ohjausjärjestelmiin.

Olla Trimatrix ™-sirun muisti

EP2S60F672C4 integroi kolmen tyyppiset RAM-lohkot (M512, M4K ja M-RAM), jotta upotettu muisti on noin 2,4 Mbit.Tämä sekoitus mahdollistaa pienten FIFO: n, keskipitkän puskurien ja suurten kaksikarjojen muistojen tehokkaasti.

Olla Omistautuneet DSP -lohkot

Laite sisältää 36 erillistä DSP -lohkoa, jotka on suunniteltu aritmeettisiin toimintoihin, kuten kertolaskuihin, kertymiseen ja FIR -suodatukseen.Nämä lohkot lisäävät suorituskykyä laskentaintensiivisissä tehtävissä säästämällä yleisiä logiikkavaroja.

Olla Nopea I/O ja signaalin eheys

Se tukee erilaisia yksipäisiä ja erilaisia I/ONämä ominaisuudet mahdollistavat vakaan, nopean tiedonsiirron jopa 1 Gbps: iin, varmistaen luotettavan viestintää ulkoisten komponenttien kanssa.

Olla Rikas ulkoinen muistirajapinnan tuki

FPGA on yhteensopiva DDR: n, DDR2: n, QDR II: n, RLDRAM II: n ja muiden muististandardien kanssa.Sisäänrakennettu käyttöliittymätuki yksinkertaistaa taulun suunnittelua ja saavuttaa korkean tiedon läpimenon muistiintensiivisiin sovelluksiin.

Olla Joustava kellonhallinta

Jopa 12 on siru-PLL: ää sallii kellon kertolaskun, jakautumisen, vaihesiirtymisen ja häiriöttömän vaihdon.Voit hienosäätää kelloa koskevia verkkotunnuksia ja vähentää värinää, tukemaan sisäisiä kellotaajuuksia jopa 500–550 MHz.

Olla Bittiä salaus ja uudelleenkonfigurointi

EP2S60F672C4 tukee AES-pohjaista bitstream-salausta immateriaalioikeuksien turvaamiseksi.Se tarjoaa myös etämuokkausominaisuuden, joka mahdollistaa kenttäpäivitykset korvaamatta laitetta.

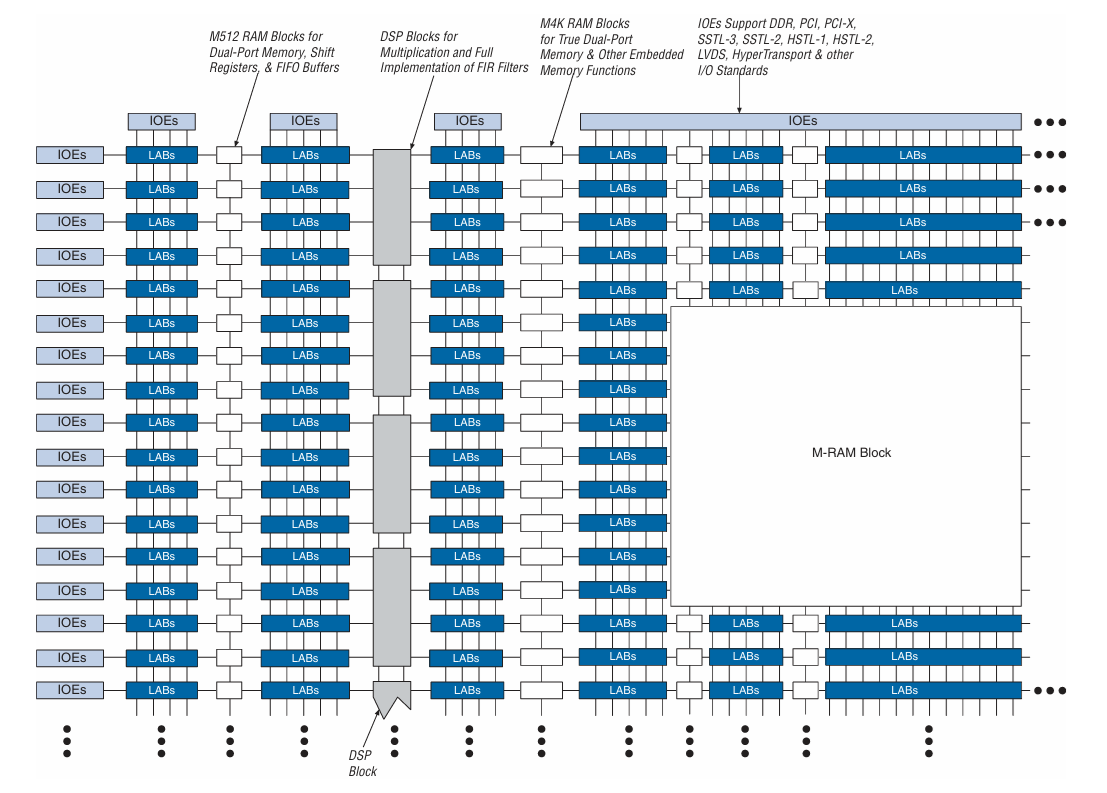

Stratix II -lohkokaavio

Stratix II -lohkokaavio, kuten EP2S60F672C4 on esitetty, kuvaa logiikan, muistin ja DSP -resurssien sisäistä järjestelyä, jotka muodostavat FPGA: n ytimen.Logic-ryhmälohkot (laboratoriot) on järjestetty tavalliseen ruudukkoon, jota ympäröivät sulautetut RAM- ja DSP-pylväät, jotka tarjoavat nopeat aritmeettiset ja sirujen säilytysominaisuudet.Perifeeriset I/O -elementit ja kelloverkot kehystävät tämän rakenteen, mikä mahdollistaa tehokkaan tiedonsiirron ja ajoitusohjauksen FPGA: n ja ulkoisten laitteiden välillä.Tämä kaavio on tärkeä, koska se auttaa ymmärtämään, kuinka erilaiset funktionaaliset lohkot ovat fyysisesti organisoituneet, jolloin ne voivat optimoida sijoittamisen, reitityksen ja järjestelmän yleisen suorituskyvyn.

Stratix II I/O Banks -kaavio

Tämä Stratix II I/O Banks -kaavio havainnollistaa, kuinka EP2S60F672C4: n tulo-/lähtötapit on ryhmitelty ja mitä sähköstandardeja kukin ryhmä tukee.Jokainen I/O -pankki on suunniteltu käsittelemään tiettyjä jännitetasoja, signalointityyppejä ja toimintoja, kuten LVTTL-, SSTL-, LVD -levyjä tai kellotulostandardeja.Asettelu osoittaa, kuinka erilaiset pankit (esim. 1, 2, 5, 6 vs. 3, 4, 7, 8 jne.) Optimoidaan joko yleiskäyttöiseen I/O: lle tai nopeaan differentiaaliseen signalointiin, mukaan lukien LVD-levyjen/LVPECL-kellotulojen tuki reunoilla.Tämän rakenteen ymmärtäminen on tärkeää nastat määritettäessä, koska oikea pankkien valinta varmistaa sähköisen yhteensopivuuden, yksinkertaistaa hallituksen reititystä ja maksimoi FPGA: n suorituskyvyn nopeassa mallissa.

EP2S60F672C4 -tekniset tiedot

|

Tyyppi |

Parametri |

|

Valmistaja |

Altera/intel |

|

Sarja |

Stratix® II |

|

Pakkaus |

Tarjotin |

|

Osien tila |

Vanhentunut |

|

Laboratorioiden lukumäärä |

3022 |

|

Logiikkaelementtien/solujen lukumäärä |

60 440 |

|

RAM -bittiä |

2 544 192 |

|

I/O: n lukumäärä |

492 |

|

Jännite - toimitus |

1,15 V ~ 1,25 V |

|

Asennustyyppi |

Pintakori |

|

Käyttölämpötila |

0 ° C ~ 85 ° C (TJ) |

|

Paketti / kotelo |

672-BBGA |

|

Toimittajan laitepaketti |

672-FBGA (27 × 27) |

|

Perustuotteenumero |

EP2S60 |

EP2S60F672C4 -sovellukset

1. Digitaalisen signaalinkäsittely (DSP) ja suodatus

EP2S60F672C4 on hyvin sopiva korkean suorituskyvyn DSP-toimintojen, kuten FIR- ja IIR-suodattimien, FFT-prosessoinnin ja monimutkaisten aritmeettisten toimintojen toteuttamiseen.Sen omistetut DSP -lohkot käsittelevät kertolaskuja ja kertymisiä tehokkaasti vapauttaen yleiset logiikkavarot muille tehtäville.On-Chip Trimatrix ™ -muisti mahdollistaa sileän datapuskuroituksen ja putkistoa, mikä on erinomainen reaaliaikaiseen prosessointiin korkealla näytteenottoasteella.Tämä tekee laitteesta ihanteellisen edistyneelle ääni-, video- ja tutka -signaalisovelluksille.

2. nopea viestintä ja verkottuminen

FPGA: n nopea I/O-rajapinnat ja dynaaminen vaiheen kohdistus (DPA) tukevat luotettavaa, gigabitin tason tiedonsiirtoa.Se voi toteuttaa viestintäprotokollat ja fyysiset kerroksen toiminnot järjestelmille, kuten reitittimille, kytkimille ja taustalevyjen yhdistämiselle.Suurella logiikkakapasiteettillaan ja joustavilla PLL: llä se pystyy hallitsemaan monimutkaisia ajoitus- ja protokollamuutoksia useiden nopean rajapinnan välillä.Nämä ominaisuudet tekevät siitä vahvan sopivan televiestinnän infrastruktuuriin ja korkean kaistanleveyden verkottumislaitteisiin.

3. Muistimäärät ja tietojenkäsittelyjärjestelmät

EP2S60F672C4 tukee erilaisia ulkoisia muistirajapintoja, mukaan lukien DDR, DDR2, RLDRAM II ja QDR II, mikä tekee siitä ihanteellisen korkean kaistanleveyden muistin ohjaimien suunnitteluun.Se pystyy käsittelemään tietojen puskurointia, osoitteiden luomista ja välimiesmenettelyä suurilla nopeuksilla pienellä latenssilla.Nopean kelloverkkojen ja sulautettujen RAM -lohkojen yhdistelmä mahdollistaa suurten tietovirtojen tehokkaan hallinnan.Tämä tekee FPGA: sta soveltuvan kuvankäsittelyyn, videon suoratoistoon ja tieteellisiin laskentaalustoihin, jotka luottavat raskaan datan läpimenoon.

4. Mukautettu logiikka ja sulautettu kiihtyvyys

Yli 60 000 logiikkaelementtiä ja rikas kellonhallinta FPGA voi isännöidä räätälöityjä laitteistokiihdyttimiä tietyille algoritmeille.Suunnittelijat käyttävät sitä usein laskennallisesti tehtävien tehtävien purkamiseen, kuten salaus, protokollan jäsentäminen tai reaaliaikainen ohjaussilmukka.Se voi myös integroida useita funktionaalisia lohkoja, joten se sopii monimutkaisiin SOC-kaltaisiin malleihin.Tämä joustavuus tekee siitä arvokkaan sovelluksissa, kuten teollisuusautomaatio, turvajärjestelmät ja ilmailualan hallintayksiköt.

5. Prototyyppien ja koulutuksen kehittämisalustat

EP2S60 -laitetta löytyy yleisesti FPGA -kehityssarjoista, joita käytetään prototyyppien, testauksen ja akateemiseen tutkimukseen.Sen logiikkakapasiteetin, I/O -määrän ja DSP -ominaisuuksien tasapaino antaa insinööreille ja opiskelijoille mahdollisuuden toteuttaa ja tarkistaa kokonaiset järjestelmät yhdellä sirulla.Se tukee digitaalisten mallien nopeaa iteraatiota, mikä mahdollistaa laitteiston todentamisen ennen sitoutumista ASIC -kehitykseen.Monet yliopistot ja T & K -laboratoriot käyttävät sitä edistyneen digitaalisen suunnittelun ja signaalinkäsittelykonseptien opettamiseen.

EP2S60F672C4 Samankaltaiset osat

|

Eritelmä |

EP2S60F672C4 |

EP2S60F672C3N |

EP2S60F672C5 |

EP2S60F672C5N |

EP2S60F672I4

|

EP2S60F672I3N |

|

Perhe / sarja |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

|

Logiikkaelementit (LE) |

60 440 |

60 440 |

60 440 |

60 440 |

60 440 |

60 440 |

|

Almut |

24 176 |

24 176 |

24 176 |

24 176 |

24 176 |

24 176 |

|

Paketti |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

|

Nopeusluokka |

C4 (STD) |

C3 (nopeampi) |

C5 (nopeampi) |

C5 (nopeampi) |

I4 (std) |

I3 (nopeampi) |

|

Lämpötila -aste |

Kaupallinen (0 ~ 70 ° C) |

Kaupallinen |

Kaupallinen |

Kaupallinen |

Teollinen (−40 ~ 100 ° C) |

Teollinen (−40 ~ 100 ° C) |

|

I/O -nastat |

492 |

492 |

492 |

492 |

492 |

492 |

|

Siru-muisti |

2,4 Mbit |

2,4 Mbit |

2,4 Mbit |

2,4 Mbit |

2,4 Mbit |

2,4 Mbit |

|

Ydinjännite |

1,2 V |

1,2 V |

1,2 V |

1,2 V |

1,2 V |

1,2 V |

|

Keskeinen ero |

Kaupallisen nopeuden perustaso |

C3 Speed Bin, lyijytön “N” |

Korkeamman nopeuden roskakori |

Suurempi nopeus, “N” -variantti |

Teollisuuslämpötila, sama tiheys |

Teollisuus, nopeampi nopeus, lyijytön |

EP2S60F672C4 -ohjelmointivaiheet

Ennen kuin voit käyttää EP2S60F672C4 FPGA -sovellusta suunnittelussa, sinun on määritettävä se oikein koottulla bittReam -alueellasi.Tämä prosessi sisältää ohjelmointitiedoston valmistelun, laitteistorajapinnan asettamisen ja sen varmistamisen, että kokoonpano latautuu oikein virtauksen yhteydessä.

Vaihe 1: Luo ja käännä malli

Aloitat kehittämällä logiikkasuunnittelua käyttämällä Intel Quartus II -ohjelmistoa.Suunnittelun valmistumisen jälkeen koota sen luodaksesi ohjelmointitiedoston (.shof tai .POF) erityisesti EP2S60F672C4 -laitteelle.Kokoonpanoprosessi tarkistaa ajoituksen, PIN -tehtävien ja resurssien käytön varmistamiseksi, että suunnittelusi sopii FPGA: n arkkitehtuuriin.Kun bittReam on koottu, se on valmis laitteen kokoonpanoon.

Vaihe 2: Aseta ohjelmointilaitteisto

Seuraavaksi valmistelet fyysisen ohjelmointirajapinnan tietokoneen ja FPGA -kortin välillä.Tyypillisesti tähän sisältyy USB-blasterin tai yhteensopivan JTAG-kaapelin kytkeminen laitteen JTAG-porttiin.Sinun on varmistettava, että Quartus II tunnistaa ohjelmoijan ja että kohdeasetus havaitaan oikein.Tämä vaihe varmistaa vakaan viestinnän ennen kokoonpanoprosessin aloittamista.

Vaihe 3: Lataa ohjelmointitiedosto laitteeseen

Lisäät kvartus II -ohjelmoijan työkalua.Sitten aloitat ohjelmointisekvenssin, jonka aikana bittivirta siirretään ja ladataan FPGA: n SRAM -konfiguraatiosoluihin.Sinun tulisi seurata edistymispalkin ja tilaviestejä vahvistaaksesi onnistuneen kokoonpanon.Kun FPGA on valmis, se alkaa suorittaa ohjelmoidun logiikan välittömästi.

Vaihe 4: Varmista kokoonpano ja toiminta

Ohjelmoinnin jälkeen varmistat, että laite toimii tarkoitetulla tavalla.Quartus II tarjoaa varmennusvaihtoehdon CRC- ja tilan signaalien tarkistamiseksi varmistaen, että malli ladataan oikein.Voit myös testata I/O -toimintojasi tai suorittaa toiminnallisen simulaation järjestelmän käyttäytymisen vahvistamiseksi.Tämä viimeinen vaihe varmistaa, että suunnittelusi on täysin toiminnassa ja vakaa laitteistossa.

EP2S60F672C4 Edut ja Haitat

Edut

• Korkea logiikkatiheys monimutkaisissa malleissa

• Hyvä suorituskyky- ja kustannussuhde

• Helppo muuttoliike samassa perheessä

• Vakaa ja kypsä kehitystyökalut

• Todistettu luotettavuus teollisessa käytössä

Haitat

• vanhentunut ja vaikeampi hankkia

• Suurempi virrankulutus kuin uudemmat FPGA: t

• Ei moderneja nopeaa lähetinvastaanottimia

• Vaikeampi ajoituksen sulkeminen suurella hyödyntämisellä

• Tulevien protokollien rajoitettu skaalautuvuus

EP2S60F672C4 Pakkausmitat

|

Tyyppi |

Parametri |

|

Pakettityyppi |

672-FBGA (Fineline BGA) |

|

Kehon koko (L × W) |

27,00 mm × 27,00 mm |

|

Paketin kokonaiskorkeus (a) |

Enintään 3,50 mm |

|

Standoff High (A1) |

Min 0,30 mm |

|

Substraatin paksuus (A2) |

Enintään 3,00 mm |

|

Pallon halkaisija (b) |

0,50 mm - 0,70 mm |

|

Pallokorkeus (e) |

1,00 mm |

|

Pallojen lukumäärä |

672 |

|

Asennustyyli |

Pintakori |

|

Pakkauskuvaus |

FBGA, 27 × 27 mm ruudukko |

EP2S60F672C4 Valmistaja

EP2S60F672C4 FPGA on valmistettu Altera Corporation, johtava edelläkävijä ohjelmoitavissa logiikkalaitteissa.Vuonna 2015 Altera osti Intel, ja tuote kuuluu nyt Intelin ohjelmoitavien ratkaisujen ryhmään (PSG), joka jatkaa Alteran vakiintuneiden FPGA -perheiden tukemista ja toimittamista.Intel ylläpitää Stratix II -linjaa osana vanhaa tuotevalikoimaaan, varmistaen dokumentoinnin, työkalujen tuen ja pitkäaikaisen saatavuuden teollisuus- ja viestintäsovelluksissa.

Johtopäätös

EP2S60F672C4 yhdistää korkean logiikan tiheyden, joustavan muistin arkkitehtuurin ja vankan I/O -ominaisuudet monimutkaisten digitaalisten järjestelmien tukemiseksi.Sen ALM-pohjainen suunnittelu, Trimatrix ™ -muisti, DSP-lohkot ja kellonhallintaominaisuudet mahdollistavat vaativien sovellusten tehokkaan toteutuksen.Vaikka se tarjoaa todistettua luotettavuutta ja kypsää kehitystukea, sillä on rajoituksia, kuten vanheneminen ja nykyaikaisten lähetinvastaanottimien puute verrattuna uudempiin FPGA -sukupolviin.Kaiken kaikkiaan sen tasapainoinen suorituskyky ja monipuolisuus tekevät siitä vankan valinnan signaalinkäsittelyyn, viestintään, tietojen käsittelyyn ja prototyyppisovelluksiin.

Tietotarvikkeet PDF

EP2S60F672C4 Datamentit:

Meistä

ALLELCO LIMITED

Lue lisää

Nopea kysely

Lähetä kysely, vastaamme heti.

Usein Kysytyt Kysymykset [FAQ]

1. Voiko EP2S60F672C4 työskennellä nykyaikaisten DDR -muistin rajapintojen kanssa?

Kyllä, se tukee DDR-, DDR2-, QDR II- ja RLDRAM II -rajapintoja, jotka kattavat monia yleisiä ulkoisia muististandardeja.Tämä tekee siitä sopivan korkean kaistanleveyden tietojenkäsittelysovelluksiin.

2. vaatiiko EP2S60F672C4 erityistä käsittelyä tai varastointia?

Kyllä, kuten muutkin BGA-pakatut komponentit, se tulisi säilyttää kosteuden ohjaamassa pakkauksessa ja käsitellä ESD-suojauksella.Oikeiden tallennuskäytäntöjen seuraaminen auttaa ylläpitämään juotettavuutta ja laitteen luotettavuutta kokoonpanon aikana.

3. Kuinka voit vähentää virrankulutusta EP2S60F672C4 -malleissa?

Voit optimoida logiikan hyödyntämisen, portin käyttämättömät kellot, alhaisemmat I/O-jännitteet mahdollisuuksien mukaan ja hyödyntää Quartus II: n tehon tietoisia synteesivaihtoehtoja kokonaistehon piirtämisen minimoimiseksi.

4. Mitä ohjelmointityökaluja tarvitaan EP2S60F672C4: lle?

Tarvitset Intel Quartus II -ohjelmistoa suunnitteluun, kokoamiseen ja ohjelmointiin sekä USB-BLASTER tai yhteensopiva JTAG-kaapeli laitteen määrittämiseen.

5. Tukeeko EP2S60F672C4-kentän päivityksiä vai etäkokoonpanoa?

Kyllä, se tukee AES-pohjaista bitstream-salausta ja etäkokoonpanoa, jolloin voit päivittää järjestelmäsi turvallisesti korvaamatta fyysisesti FPGA: ta.

Kaikki LFXP6C-3FN256C Lattice Semiconductor

06.10.2025

XC2C256-7TQ144C CPLD: PINOUT, OMINAISUUTTEET, Ohjelmointi ja tietotapaus opas

03.10.2025

Suositut viestit

-

COMPLECT -ohjeet Tietokoneet: Kuinka ne muuttivat tietojenkäsittelyä?

18.04.8000 147780

-

USB-C-pinout ja ominaisuudet

18.04.2000 112050

-

Xilinx Unified Simulation Primitive -sovelluksen käyttäminen: Kattava opas FPGA: n suunnitteluun ja simulointiin

18.04.1600 111352

-

Virtalähteen jännitteet elektroniikassa: VCC:n, VDD:n, VEE:n, VSS:n ja GND:n merkitys

18.04.0400 83806

-

RJ45 Connector Guide: Pinout, johdotus, kaapelityypit ja käyttö

01.01.1970 79608

-

Lopullinen opas johdon värikoodiin nykyaikaisissa sähköjärjestelmissä

Tapa, jolla sähköjärjestelmämme käyttävät värejä, ei ole vain ulkonäölle.Jokainen lankaväri osoittaa nyt tietyn toiminnon, mikä helpottaa sähkökomponenttien tunnistamista ja käsittelyä oikein asenn...01.01.1970 66988

-

Puhdistusventtiilin opas: Toiminta, oireet, testaus ja korvaava moottorin optimaalinen suorituskyky

Puhdistusventtiili on keskeinen osa auton järjestelmää, joka auttaa pitämään ilman puhtaana hallitsemalla polttoainehöyryjä ennen kuin ne voivat paeta ilmakehään.Tämä ei vain auta ympäristöä vähent...01.01.1970 63113

-

Laatu (Q) tekijä: Yhtälöt ja sovellukset

Laatukerroin tai 'Q' on tärkeä tarkistettaessa, kuinka hyvin induktorit ja resonaattorit toimivat elektronisissa järjestelmissä, jotka käyttävät radiotaajuuksia (RF).'Q' mittaa kuinka hyvin piiri m...01.01.1970 63049

-

Huippututkinnon saavuttaminen suurimmalla tehonsiirtolauseella

Suurin virransiirtolause selittää, kuinka energia lähteestä, kuten akku tai generaattori, virtaa kytkettyyn kuormaan.Se näyttää tarkan tilan, jossa kuorma vastaanottaa eniten virtaa.Tämä artikkeli ...01.01.1970 54097

-

A23 -akun tekniset tiedot ja yhteensopivuus

A23-akku on pieni, sylinterimainen akku, jolla on korkea jännite.Kutsutaan myös 23a, 23ae tai MN21, se toimii 12 voltilla ja paljon korkeampi kuin AA- tai AAA -akut.Sen erityinen muotoilu ...01.01.1970 52199