CPLD Selitti: Opas ohjelmoitaviin logiikkalaitteisiin

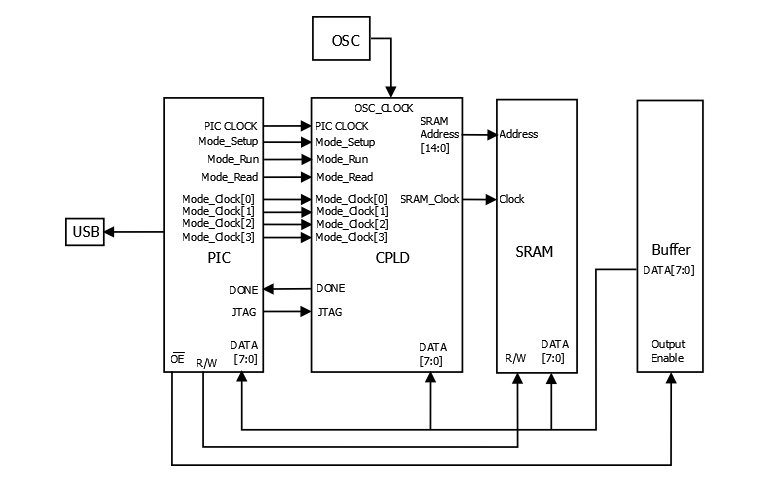

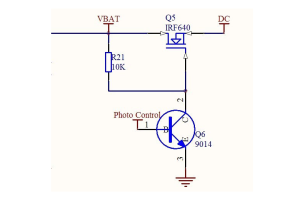

Elektronisen suunnittelun dynaamisessa maailmassa monimutkaiset ohjelmoitavat logiikkalaitteet (CPLD) erottuvat monipuolisina työkaluina, sekoittaen saumattomasti sopeutumiskykyä, tarkkuutta ja tehokkuutta.Nämä laitteet mullistivat piirisuunnittelun ottamalla käyttöön ohjelmoitavat makro -solut ja hallitsevan toisiinsa liittyvän matriisin, mikä mahdollistaa monimutkaisten logiikkafunktioiden luomisen huomattavan luotettavuuden avulla.CPLD: t ovat perustaneet 1980 -luvulla heidän avainrooliinsa nykyaikaisissa teollisuudessa, kuten verkottumisessa, autoteollisuudessa ja ilmailu- ja ilmailu- ja ilmailu-Tämä artikkeli kaivaa CPLD: n matkaa, niiden erityisiä piirteitä, käytännön sovelluksia ja ohjelmointimenetelmiä, jotka tekevät niistä kulmakiven digitaalisessa logiikan suunnittelussa.Luettelo

Yleiskatsaus CPLD: stä

Kompleksisten ohjelmoitavien logiikkalaitteiden (CPLDS) hallitsemisessa yksi löytyy ohjelmoitavien logiikka -makro -solujen hienostuneen kuvakudoksen, joka on kietoutunut hallitsevan toisiinsa liittyvän matriisin läpi.Näiden makrolisolujen (MC) ja syöttö/lähtö (I/O) -yksikköviivat antavat sinun suunnitella osaavasti piirit, jotka määrittävät ainutlaatuisten toimintojen rakenteet.Toisin kuin laitteet, jotka ovat hämmentyneitä niiden monimutkaisesta liitäntäajasta, CPLD: t käyttävät kiinteää metallilanaa.Tämä ominaisuus antaa heille johdonmukaisen ja ennakoitavissa olevan kellonkäyttäytymisen, mikä tekee ajoitusennusteista luotettavampia ja tarkempia.

Matka ja käyttö

1970 -luvulla julisti ohjelmoitavien logiikkalaitteiden (PLD) tulemisen edistäen siirtymistä kohti ohjelmoitavia makroyksiköitä.Tämä muutos esitteli runsaasti suunnittelun joustavuutta, erottaen ne staattisista digitaalisista piireistä, vaikka niiden hyödyllisyys oli alun perin rajoitettu yksinkertaisempiin piireihin.CPLDS: n tulo 1980-luvun puolivälissä mullisti tämän maiseman tasoittaen tietä monimutkaisille piirimalleille.Siitä lähtien he ovat kudottuja teollisuudenaloihin, kuten verkottumiseen, autoelektroniikka-, CNC -koneistus- ja ilmailu- ja avaruusjärjestelmiin.Voit muistaa tapaa, jolla CPLDS yksinkertaisti prosesseja, jotka kerran vaativat huolellista käsityötä, mikä merkitsee huomattavaa tehokkuuden hyppyä.

CPLDS: n erottuvat ominaisuudet

CPLD: t erottuvat sopeutuvan ohjelmoinnin, laajan integraation, nopean kehitysominaisuuksiensa ja laaja-alaisen sovellettavuuden sekä taloudellisten tuotantokustannusten kanssa.He vetoavat niihin, joilla on minimaalinen laitteistokokemus ja jotka toimivat luotettavina ja turvallisina tuotteina, jotka eivät vaadi tyhjentävää testausta.CPLDS: llä on todistus heidän kyvykkyydestään laajamittaisissa piirimalleissa prototyyppien kehittämisessä ja palvelevat alle 10 000 yksikköä, mikä ilmentää sinulle hyödyllistä pätevyyttä.CPLDS: n sopeutumisprojektin vaatimuksiin sopeutuminen ansaitsee heille usein arvostusta korostaen niiden todellista monipuolisuutta dynaamisissa ympäristöissä.

Sovellusmenetelmät

Näiden integroitujen piirien avulla voit selvittää heidän tarpeisiinsa räätälöityjä logiikkatoimintoja sekä kaavioiden että laitteistojen kuvauskielten avulla kehitysalustoilla.Esimerkiksi vastaavakoneen suunnittelussa valmistetaan ja kootaan tietokoneelle.Lataa kaapelia hyödyntämällä koodi siirretään CPLD: lle järjestelmän sisäistä ohjelmointia varten, joka käsittää testauksen, vianetsinnän ja parantamisen.Sitten onnistuneesti muotoiltuja malleja tuotetaan massatuotantoa kopioimalla CPLD-sirut.Projekteissa, kuten Traffic Light Systems, suunnitteluprosessin toistamisesta tulee välttämätöntä, samanlainen kuin talon uudelleenrakentaminen sen uusimisen palauttamiseksi.Tämä toistuva menetelmä luo usein perustan sekä taitojen että luottamuksen hallitsemiseksi, lisäämiseksi.

Johtavat variantit

Alteran, hilan ja Xilinxin kaltaiset yritykset ovat vuosien varrella paljastaneet näkyviä CPLD -linjoja.Huomionarvoisia esimerkkejä ovat Alteran EPM7128s, Hila LC4128Vja Xilinxin XC95108 .Nämä mallit ovat löytäneet näkyviä rooleja monissa globaaleissa sovelluksissa.Ne, joilla on ollut etuoikeus työskennellä näiden erillisten tuotteiden kanssa, huomauttavat usein hienovaraisista, mutta tehokkaista eroista, jotka optimoivat tiettyjä toimintoja.Tämä heijastaa hienoa valintaprosessia, johon erityiset projektivaatimukset vaikuttavat, missä jokainen variantti ottaa ainutlaatuisen vetoomuksensa.

FPGA: n ja CPLD: n tunnistaminen ja luokittelu

|

Näkökohta |

CPLD |

FPGA |

|

Loogisen käyttäytymisen muodostuminen |

Muodosta looginen käyttäytyminen tuoteraalirakenteen avulla.

Esimerkkejä: Lattice ISPLSI -sarja, Xilinx XC9500 -sarja, Altera Max7000s

Sarja, Lattice Mach -sarja |

Muodosta looginen käyttäytyminen taulukon hakumenetelmällä.

Esimerkkejä: Xilinx Spartan -sarja, Altera Flex10K, ACEX1K -sarja |

|

Soveltuvuus |

Sopii algoritmeihin ja yhdistelmälogiikkaan, toimii

Parempi rajoitetuilla liipaisimilla ja rikkailla tuotetermeillä |

Sopii peräkkäiseen logiikkaan, toimii paremmin

liipaisimissa runsaasti rakennetta |

|

Ajoitusviive |

Jatkuva johdotusrakenne tarjoaa yhtenäisen ja

Ennustettavat ajoitusviiveet |

Segmentoitu johdotusrakenne johtaa arvaamattomaan ajoitukseen

viivästykset |

|

Ohjelmoinnin joustavuus |

Kiinteät sisäpiirit muokataan ohjelmointia varten.

Logic-lohkotason ohjelmointia käytetään |

Sisäistä johdotusta on muokattu ohjelmointia varten.Logiikka

Porttitason ohjelmointi mahdollistaa suuremman joustavuuden |

|

Integrointi |

Alempi integraatio verrattuna FPGA: hon |

Korkeampi integraatio monimutkaisempaan johdotusrakenteeseen ja

logiikan toteutus |

|

Helppokäyttöisyys |

Helpompi käyttää ohjelmointia E2PROM: n tai FastFlashin kautta.

Ulkoista muistisirua ei tarvita |

Vaatii ulkoisen muistin ohjelmoinnin tallentamiseksi

Tiedot, mikä johtaa monimutkaisempaan käyttöön |

|

Nopeus ja ennustettavuus |

Nopeampi nopeus ja parempi ajoituksen ennustettavuus

logiikkalohkojen välinen yhdistäminen |

Hitaampi nopeus ja vähemmän ennustettavissa oleva ajoitus

Porttitason ohjelmointi ja hajautettu yhteenliittäminen |

|

Ohjelmointitekniikka |

Käyttää E2PROM- tai Flash -muistin ohjelmointia.Ohjelmointitiedot

säilytetään, kun järjestelmä on virta.Tukee ohjelmointia a

ohjelmoija tai järjestelmä |

Perustuu SRAM -ohjelmointiin.Ohjelmointitiedot menetetään, kun

Järjestelmä on virta ja se on ladattava uudelleen.Tukee dynaamista

kokoonpano |

|

Luottamuksellisuus |

Tarjoaa parempaa luottamuksellisuutta |

Tarjoaa alhaisemman luottamuksellisuuden |

|

Virrankulutus |

Yleensä suurempi virrankulutus, etenkin

korkeampi integraatio |

Pienempi virrankulutus CPLD: hen verrattuna |

CPLD: n ohjelmointikielet

Analysoidaan, kuinka monimutkaiset ohjelmoitavat logiikkalaitteet (CPLD) ohjelmoitu on kulmakivi monipuolisten laitteistoratkaisujen asettamisessa.CPLD: n ohjelmointihistorialliset menetelmät ovat luottaneet tikkaat kaavioihin tai laitteistokuvauskieliin (HDLS), ja Verilog HDL ja VHDL ovat pääasiallisia valintoja.Valittu kieli voi muokata sekä suunnittelustrategiaa että toteutuksen toiminnan tehokkuutta.

Olla Verilog HDL: Verilog HDL: tä on vaalittu yksinkertaisesta syntaksistaan ja vankista simulaatioominaisuuksistaan, mikä heijastaa digitaalisessa logiikan suunnittelussa käytettyjä menetelmiä.Sen integrointi elektronisen suunnittelun automaation (EDA) työkalujen avulla voit suorittaa saumattomasti synteesiä ja simulointia.Verilogin C-kaltaisen syntaksin on havaittu vähentävän pääsyn esteitä niille, joilla on ohjelmointitausta, kiirehtimällä matkaa suunnittelusta käyttöönottoon monenlaisten teollisuussektoreiden välillä.

Olla VHDL: VHDL tarjoaa yksityiskohtaisemman ja ilmaisullisen vaihtoehdon HDL -ohjelmointiin.Usein valinta hankkeille, jotka vaativat huolellista dokumentaatiota ja tiukkaa tyypin tarkistamista, ilmailu- ja puolustusteollisuudessa arvostettuja piirteitä.Voit huomata, että huolimatta VHDL: n potentiaalisesta monimutkaisuudesta pienemmissä projekteissa, sen kurinalainen rakenne tukee poikkeuksellisen luotettavien kuvioiden luomista, välttämättömyyttä ympäristöissä, joissa turvallisuus on hallitsevaa.

Meistä

ALLELCO LIMITED

Lue lisää

Nopea kysely

Lähetä kysely, vastaamme heti.

NMOS -transistorit: suunnittelu, toiminta ja sovellukset

29.12.2024

Fast Fourier -muunnos (FFT): Digitaalisen signaalinkäsittelyn mullistaminen

29.12.2024

Suositut viestit

-

COMPLECT -ohjeet Tietokoneet: Kuinka ne muuttivat tietojenkäsittelyä?

17.04.8000 147719

-

USB-C-pinout ja ominaisuudet

17.04.2000 111777

-

Xilinx Unified Simulation Primitive -sovelluksen käyttäminen: Kattava opas FPGA: n suunnitteluun ja simulointiin

17.04.1600 111327

-

Virtalähteen jännitteet elektroniikassa: VCC:n, VDD:n, VEE:n, VSS:n ja GND:n merkitys

17.04.0400 83645

-

RJ45 Connector Guide: Pinout, johdotus, kaapelityypit ja käyttö

01.01.1970 79327

-

Lopullinen opas johdon värikoodiin nykyaikaisissa sähköjärjestelmissä

Tapa, jolla sähköjärjestelmämme käyttävät värejä, ei ole vain ulkonäölle.Jokainen lankaväri osoittaa nyt tietyn toiminnon, mikä helpottaa sähkökomponenttien tunnistamista ja käsittelyä oikein asenn...01.01.1970 66802

-

Laatu (Q) tekijä: Yhtälöt ja sovellukset

Laatukerroin tai 'Q' on tärkeä tarkistettaessa, kuinka hyvin induktorit ja resonaattorit toimivat elektronisissa järjestelmissä, jotka käyttävät radiotaajuuksia (RF).'Q' mittaa kuinka hyvin piiri m...01.01.1970 62965

-

Puhdistusventtiilin opas: Toiminta, oireet, testaus ja korvaava moottorin optimaalinen suorituskyky

Puhdistusventtiili on keskeinen osa auton järjestelmää, joka auttaa pitämään ilman puhtaana hallitsemalla polttoainehöyryjä ennen kuin ne voivat paeta ilmakehään.Tämä ei vain auta ympäristöä vähent...01.01.1970 62854

-

Huippututkinnon saavuttaminen suurimmalla tehonsiirtolauseella

Suurin virransiirtolause selittää, kuinka energia lähteestä, kuten akku tai generaattori, virtaa kytkettyyn kuormaan.Se näyttää tarkan tilan, jossa kuorma vastaanottaa eniten virtaa.Tämä artikkeli ...01.01.1970 54045

-

A23 -akun tekniset tiedot ja yhteensopivuus

A23-akku on pieni, sylinterimainen akku, jolla on korkea jännite.Kutsutaan myös 23a, 23ae tai MN21, se toimii 12 voltilla ja paljon korkeampi kuin AA- tai AAA -akut.Sen erityinen muotoilu ...01.01.1970 52029